CISC & RISC

태그 :

- 개념

- CISC(Complex Instruction Set Computer)의 정의. 연산에 처리되는 복잡한 명령어들을 수백 개 이상 탑재하고 있는 프로세서. 마이크로 프로그래밍을 통해 사용자가 작성하는 고급언어에 각각 하나씩 기계어를 대응시킨 회로로 구성된, 중앙처리장치의 한 종류. RISC(Reduced Instruction Set Computer)의 정의. 복잡한 80%명령어를 제거하여 사용빈도가 높은 명령어 위주로 20%의 명령어를 H/W화하여 처리속도를 향상시킨 프로세서. 컴퓨터의 실행속도를 높이기 위해 복잡한 처리는 소프트웨어에게 맡기는 방법을 채택하여, 명령세트를 축소 설계한 컴퓨터

I. . Instruction Set의 개요

가. 정의

- Computer Hardware가 직접 해독∙실행이 가능한 명령어 집합

나. Instruction Set의 설계 목표

- 효율적인 Implementation을 통해 속도 최적화

- Instruction Field의 효율적 사용

다. Instruction Set 적용 분류 - Microprocessor

|

분류 |

내용 |

|

CISC |

Complex Instruction Set Computer 전통적 Von Neumann 방식의 명령어 내장 방식 컴퓨터가 지원하는 명령어가 많을수록 프로그램내의 Instruction count는 줄어듬 명령어의 길이가 상이 함 Micro programming control |

|

RISC |

Reduced Instruction Set Computer 자주 사용하지 않는 명령어 제거 및 단순화 모든 명령어의 길이를 일정하게 만듬 하나의 Cycle에 여러 명령어 수행 Hardwired control |

II. CPU의 명령어 처리 및 구성 방식, CISC & RISC의 개요.

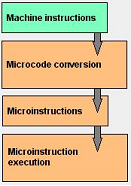

가. CISC(Complex Instruction Set Computer)의 정의.

- 연산에 처리되는 복잡한 명령어들을 수백 개 이상 탑재하고 있는 프로세서

- 마이크로 프로그래밍을 통해 사용자가 작성하는 고급언어에 각각 하나씩 기계어를 대응시킨 회로로 구성된, 중앙처리장치의 한 종류

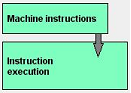

나. RISC(Reduced Instruction Set Computer)의 정의.

- 복잡한 80%명령어를 제거하여 사용빈도가 높은 명령어 위주로 20%의 명령어를 H/W화하여 처리속도를 향상시킨 프로세서

- 컴퓨터의 실행속도를 높이기 위해 복잡한 처리는 소프트웨어에게 맡기는 방법을 채택하여, 명령세트를 축소 설계한 컴퓨터

III. CISC와 RISC의 구성도 및 구성요소.

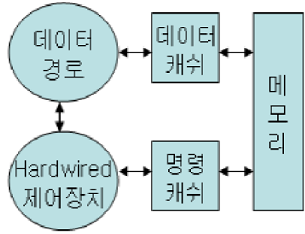

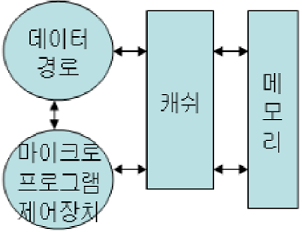

가. RISC 및 CISC의 구조 및 명령처리 순서.

|

구분 |

RISC |

CISC |

|

구성 |

|

|

|

명령 처리 순서 |

|

|

나. RISC 및 CISC의 구성요소

|

구분 |

상세 설명 |

|

|

메모리 |

주 기억장치 |

일반적으로 RAM을 말하며 프로그램의 실행 시 보조기억장치로부터 데이터를 읽어오는 역할을 한다. |

|

보조 기억장치 |

주기억장치를 보조하기 위한 역할로 데이터의 영구적인 저장이 주목적이며, 주로 사용되는 제품으로는 HDD, TAPE, ODD가 있다 |

|

|

가상 기억장치 |

대부분 보조 기억장치로 주기억장치처럼 동작 할 수 있도록 하는, 가상 기억장치로 |

|

|

Cache (CISC) |

L1 Cache (CISC) |

CPU 내의 캐쉬 메모리로 고속의 속도와 높은 가격이 특징이며 주목적은 메모리와 CPU간의 병목현상의 해결 |

|

L2 Cache(RISC) |

CPU와 주기억장치 사이에 위치하는 캐쉬로 일반적으로 메인보드에 위치 하고 있으며 L1 캐쉬와 비교 시 낮은 성능(속도)와 낮은 가격을 형성하고 있으나 주기억장치와 비교 시 월등하게 높은 가격과 높은 성능을 가지고 있다. |

|

|

Cache (RISC) |

Data Cache |

CPU의 데이터 처리를 위한 전용 캐쉬 메모리로 RISC의 경우 CISC와 비교하여 캐쉬의 용량과 성능이 더욱 뛰어 나며 이것은 CPU의 가격상승으로 연결된다. |

|

명령 Cache |

CPU의 명령어 처리를 위한 전용 캐쉬 메모리로 RISC의 경우 파이프 라인 구조로 처리시 CISC와 비교 시 높은 성능의 향상 을 가져오게 된다. |

|

|

데이터 경로 (BUS) |

내부, 외부, 데이터, 주소, 제어 BUS |

데이터가 전송되는 경로를 뜻하며 쉬운 개념으로 회로의 전선으로 표현될 수 있다. 프로세스 내부의 처리는 내부 BUS가 처리하며 프로세서 밖의 처리는 외부 BUS가 처리하게 된다. 그 외에 데이터 BUS, 주소 BUS, 제어 BUS로 나눌 수 있다. |

다. CISC & RISC 비교

|

구분 |

CISC |

RISC |

|

아키텍쳐 히스토리 |

대용량 컴퓨터를 중심으로 1960년대 중반부터 개발됨 |

-32비트 아키텍쳐로 1950년대부터 개발됨 -Load/store 구조 -1995:코드압축 RISC 개발됨 |

|

명령어구조 |

복잡 |

단순 |

|

프로그램 코드 사이즈 |

소규모(130~140) |

큼(160~180 |

|

성능 |

낮음 |

높음 |

|

임베디드 |

가능 |

불가능 |

|

약점 |

-명령어구조와 하드웨어 복잡 -64비트 아키텍쳐 개발 어려움 |

-16비트 아키텍쳐 개발 어려움 -낮은 효율성으로 64비트로 Migration 어려움 |

IV. 프로세서의 종류 구분.

가. 데이터 버스 크기에 따른 분류

- 데이터 버스의 크기에 따라 분류되며 대부분 아래와 같이 분류가 가능.

|

8비트 |

16비트 |

32비트 |

64비트 |

|

초소형의 시스템에 사용되며 소형의 Embedded 시스템에 많음 |

SBC(Single Board Computer)에서 많이 사용되며 중형/대형의 Embedded 시스템에서 사용 |

현재 많이 사용되는 PC용 CPU들이 주를 이루고 있음 |

서버용으로 제공되는 CPU들이 64bit BUS를 많이 사용함 |

나. Byte ordering에 따른 분류

- 메모리에 저장될 때 바이트의 순서에 따른 분류를 말하며 아래의 두 가지로 분류할 수 있다

|

항 목 |

Little Endian |

Big Endian |

|

분류 방법 |

하위 바이트의 값이 메모리에 먼저 표시되는 방식이며 메모리의 가장 높은 주소부터 데이터를 채워가는 방식 |

상위 바이트의 값이 메모리에 먼저 표시되는 방식이며 메모리의 가장 낮은 주소부터 데이터를 채워가는 방식 |

|

장점 |

산술 연산이 빠르다 |

가 독성이 뛰어나고 대소비교가 빠르다 |

|

제품 |

Intel X86계열 |

Sun, 모토로라 계열 |

다. ISA(Instruction Set Architecture)의 복잡도에 따른 분류

- 명령어 Set 구조에 따른 분류를 나타내며 CISC, RISC로 나눌 수 있다.

|

항 목 |

CISC |

RISC |

|

명령어 |

명령어 개수가 많고 그 길이가 다양 하며 실행사이클도 각각 다름 |

명령어 수가 적고 길이가 고정적, 워드와 데이터버스 크기가 동일, 실행사이클도 모두 동일 |

|

레지스터 |

소수레지스터 |

다중레지스터 사용 및 최적화 |

|

메모리 |

많은 명령어가 메모리를 참조 |

메모리는 Load, Store명령만 처리 |

|

파이프 라이닝 |

파이프라이닝 기법을 사용하기 어려움 |

파이프라이닝을 사용하기 쉽고 많이 사용, 슈퍼 스칼라 |

|

제어방식 |

마이크로 프로그래싱 제어 |

Hardwired control |

|

컴파일러 |

컴파일러가 복잡함 컴파일작업 실행 시 RISC와 비교하여 Binary 코드의 길이가 짧다 |

단순한 컴파일러 구현 가능 컴파일작업 실행 시 CISC와 비교하여 Binary 코드의 길이가 길다 |

|

회로구성 |

복잡함 |

단순함 |

|

프로그램 |

비교적 적게 명령어를 사용하여 결과를 얻을 수 있음 |

명령어가 적고 단순하므로 많은 수의 명령어가 조합되어 사용 |

|

사용환경 |

호환성이 중요한 환경 |

단순한 명령이 반복적으로 많이 사용되고 빠르게 처리되는 환경 |

V. CISC와 RISC의 장점을 절충한 EISC

가. EISC(Extendable Instruction Set Computer)의 정의

- Embedded 프로세서용으로 개발된 RISC기반의 명령어 집합으로 RISC의 결성과 CISC의 확장 성을 동시에 가짐으로 장점을 절충한 형태의 프로세서

나. EISC의 명령어 특징

|

항 목 |

내용 및 특징 |

|

명령어 필드 지정 |

RISC 프로세서는 명령어 지정에 있어서 고정필드 형태의 명령어를 사용하며 명령어 해독이 간편하지만 EISC프로세서는 그 명령어의 필드 지정이 매우 복잡하다. 복잡한 명령의 사용은 각각의 명령어에 따라 필요한 필드를 더 효율적으로 배정한 것이기 때문에 코드밀도가 높다 |

|

고정길이 명령어 |

가변길이 명령어인 CISC와 달리 EISC는 고정길이 명령어를 사용하고 있고 그에 따라 명령어 해석기의 구조가 간단하다. |

| 즉시 데이터와 오프셋의 확장 | EISC는 ISA수준에서 즉시 데이터의 확장을 지원하며, RISC와 달리 즉시 데이터의 값을 직접적으로 사용할 수 있게 하는 특수목적 레지스터와 명령어가 있다. |

다. 프로세서의 종류

- EISC 프로세서의 종류는 ISA구성에 따라 SE(Simple EISC)와 AE(Advanced EISC)로 나뉜다

|

항 목 |

Simple EISC |

Advanced EISC |

|

코어 |

SE1608 / SE3208 |

AE32000C-Tiny/-Lucida/-Empress |

|

프로세서 |

16Bit CPU / 32Bit CPU |

32Bit CPU |

|

파이프 라인 |

3Stage |

3 Stage / 5 Stage / 9 Stage |

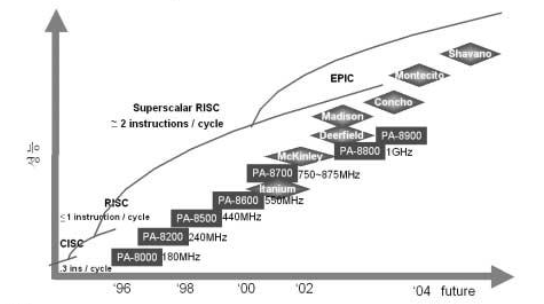

VI. 병렬 명령처리가 가능한 병렬처리 컴퓨터, EPIC의 개요

가. EPIC(Explicitly Parallel Instruction Computing)의 정의

- 사용장의 컴파일러가 소스 코드로부터 병렬 성을 찾아내고 병렬처리용 기계어 코드를 생성하여 수행하는 방식

- VLIW(Very Long Instruction Word) 방식에 기반을 둔 명령 처리 방식

나. EPIC의 특징

- 기계어 수준에서의 향상된 병렬화, 메모리 사용 시 줄어든 대기 시간

- 최적화 된 리소스 사용으로 인한 프로그램 내 분기 문의 효율적인 처리

- 향상된 실수 연산, 함수 처리 시 줄어 든 오버헤드

- 장점: 다중운영체제지원, 인스트럭션 구조 간단, 작은 프로그램 사이즈, 성능우수, 저전력 소모, Embedded 시스템에 적합

- 단점: 컴파일러에서 동시에 실행해야 할 2개 이상의 명령어를 명시적으로 표현해야 하므로 컴파일러 성능이 좋아야 함

다. EPIC의 구성 및 비교

- EPIC의 구성

- 명시적인 병렬화는 명령어를 다른 동작에 관계없이 처리 할 수 있는 경우에 컴파일러가 알려줌

- EPIC과 타 방식의 비교

|

구분 |

CISC |

RISC |

EPIC |

|

처리속도 |

1/3명령어/clock |

1명령어/clock |

2명령어이상/clock |

|

등장시기 |

1980년대 |

1980년 후반 |

1990년대 초반 |

|

개요 |

최소명령어 길이 |

긴 명령어 길이 |

명령어 병렬처리 |

|

특징 |

CPU 구조 복잡 |

신뢰성 향상 |

명령어 수행 |

|

제품 |

X86계열 |

RS/6000 Alpha칩 |

HP IA-64 |