DMA (Cycle Stealing)

태그 :

- 개념

- 메모리 버퍼, 포인터, 카운터를 사용하여 장치 제어기가 CPU의 도움 없이 DMA컨트롤러를 이용하여 데이터를 직접 메모리로 전송하는 입출력 방식

I. CPU의 도움없이 I/O 장치가 직접 메모리에 접근하는 방식, DMA의 개요

가. Direct Memory Access의 정의

- 메모리 버퍼, 포인터, 카운터를 사용하여 장치 제어기가 CPU의 도움 없이 DMA컨트롤러를 이용하여 데이터를 직접 메모리로 전송하는 입출력 방식

- CPU는 상태, 제어정보만을 교환하고 데이터 전송은 I/O와 메모리간에 직접 교환

- DMA컨트롤러가 버스를 제어하고 I/O와 메모리가 정보를 직접 전송

- 중앙처리장치에게 PIO작업을 할당하지 않고 DMA라는 특수 프로세서에게 위임하여 메모리와 직접 데이터 전송할 수 있도록 하는 방법

나. 등장배경(인터럽트 오버헤드)

- 고속의 I/O 장치의 경우 인터럽트로 CPU의 실제적인 프로세스 작업 시간 감소

- 디스크 같은 많은 데이터를 입/출력하는 장치를 위해 범용 프로세서가 매번 전송을 제어하게 하는 것은 낭비

- 인터럽트 방식이 프로그램에 의한 입출력 방식보다는 효율적이지만 입출력을 위한 상태, 제어정보,데이터 전송을 위해서는 능동적인 CPU의 개입이 필요하기 때문에 오버헤드 발생 가능

다. DMA의 특징

- 프로그램 수행 중 인터럽트의 발생 횟수 최소화하여 시스템 효율 증대

- CPU는 DMA 컨트롤러와 상태정보 및 제어 정보만 전송

- CPU의 개입 없이 입출력장치와 주 기억 장치와의 데이터 직접 전송

라. PC 입출력 방식의 유형

|

유형 |

설명 |

|

Programmed I/O |

Port를 이용한 데이터 전송, 프로그램에 의해 제어됨 주변장치의 상태가 준비상태가 될 때 까지 CPU는 대기상태 |

|

Interrupt Driven I/O |

입출력 인터페이스가 주변장치 상태 값을 요청 준비상태가 되면 인터럽트 신호가 구동되어 CPU에 I/O를 요청 |

|

DMA |

CPU의 직접적인 개입 없이 I/O 장치와 Memory 사이의 데이터 전송을 담당하는 제어기를 사용 |

II. DMA의 구성도 및 동작 방식

가. DMA의 구성도

나. DMA 동작방식

① I/O 인터페이스가 DMA 컨트롤러에게 DMA 서비스를 요청을 전송

② CPU의 HOLD Pin에 Bus Request가 전송되어 버스에 대한 제어를 DMA가 획득 (Active High)

③ CPU의 HLDA(Hold Acknowledge) Pin으로부터 DMAC에 Bus grant가 리턴됨 (Active High)

④ DMAC는 Address bus에 Address Register의 Contents를 적재한다

⑤ DMAC는 I/O Interface에게 데이터를 데이터버스에 적재하도록 DMA Acknowledgement를 전송한다

⑥ Data Byte가 Address Bus에 의해 식별된 메모리 위치로 전송된다.

⑦ I/O Interface는 데이터를 지속적으로 전송유지 한다 (Latch)

⑧ Bus Request 가 Drop되어 HOLD가 Low 상태가 되어 DMAC는 Bus에 대한 사용권을 돌려준다.

⑨ BUS Grant가 Drop되어 HLDA가 Low 상태가 된다

⑩ 이후, Address Register가 1 증가되고, Byte Count는 1 감소된다

⑪ Byte Count가 0이 아니면 Step ①로, 0이면 정지

(출처: http://www.electronics.dit.ie/staff/tscarff/DMA/dma.htm)

III. DMA 동작모드 및 컨트롤러 구성

가. DMA의 동작모드

|

구분 |

설명 |

|

사이클스틸링 (Cycle Stealing) |

|

|

버스트모드 (Burst mode) |

|

나. DMA 컨트롤러 구성

- DMA(Direct Memory Access) 컨트롤러는 CPU나 I/O 디바이스와 통신하기 위해서 일반적인 인터페이스 회로를 필요로 함

- Address Register, Word Count Register, Single Set Address Line이 필요

|

구분 |

구성 |

설명 |

|

명령어 |

DMA Select(DS)/ Register Select(RS) |

CPU가 Address Bus를 통해 DS와 RS 입력을 enable 시킴으로써 DMA Register를 선택 |

|

Bus Request(BR) |

버스요구입력은 DMA컨트롤러를 통해 CPU 버스 제어를 양도하도록 요구하는 신호 BR입력이 들어오면 CPU는 어드레스 버스, 데이터 버스 와 I/O라인을 고임피던스상태로 변경 |

|

|

Bus Grant(BG) |

BR요구로 인한 상태 변경 후 CPU는 버스 허용 출력 을 DMA컨트롤러에 보내 DMA버스 가능함을 알림 BG라인을 enable하면 외부 DMA컨트롤러는 메모리 와 직접 통신을 하기 위해 버스 시스템을 제어 |

|

|

레지스터 |

Address resister |

메모리의 접근할 주소를 저장 Address Bit들은 버퍼를 통하여 Address Bus로 전송 매 Work가 전송될 때마다 H/W에 의해 Increment됨 |

|

Word count register |

전송할 블록의 Word수를 저장 매Word가 전송될 떄마다 H/W에 의해 Decrement됨 각 워드 전송 시마다 감소되며 O인가를 점검 |

|

|

Control register |

DMA의 모든 레지스터가 CPU에게는 I/O인터페이스 레지스터, 동작 모드 설정(버스트 전송, 사이클 스틸링) |

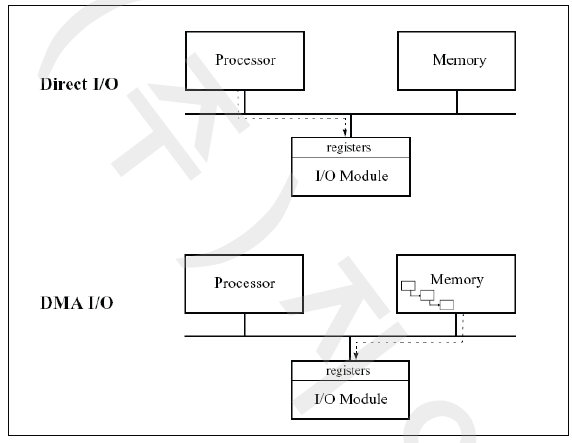

- DMA 를 사용하면 DMA 를 통하여, 원하는 data 가 disk 에서 memory 로 load 가 되고 CPU 는 다른 프로세스를 처리할 수 있지만, DMA 가 없는 Direct I/O 의 경우에는 CPU 에서 disk I/O 가 완료될 때까지 다른 작업을 처리하지 못하고 오랜 시간을 CPU 가 대기해야 함

IV. 비교표

가. Polling과 Interrupt와의 비교

|

Polling |

Interrupt |

Cycle Stealing |

|

|

|

나. DMA와 채널 방식의 비교

|

구분 |

Channel에 의한 I/O |

DMA에 의한 I/O |

|

개념 |

|

|

|

차이점 |

|

|

|

공통 |

|

|

V. Direct I/O와 DMA의 기능 및 특징 비교

가. Direct I/O와 DMA의 기능에 개념적인 I/O 비교

나. Direct I/O와 DMA의 장단점 비교

|

구분 |

DMA |

Direct I/O |

|

장점 |

|

|

|

단점 |

|

|

VI. DMA외의 여러 가지 입출력 방식

가. Programmed Driven I/O

- CPU상에서 실행되는 프로그램에 의해 입출력이 제어되는 방식

- CPU는 입출력장치에게 명령 송신 후 동작완료 시 까지 대기

- CPU는 주기적으로 주변 장치의 상태를 검사하여 실제 요청이 된 상태의 디바이스 점검

- CPU의 비효율적인 동작과 자원 낭비 발생

나. Interrupt Driven I/O

- I/O 인터페이스가 주변 장치의 Status를 체크하여 준비 상태 시 인터럽트 신호를 발생 CPU에게 입출력 처리를 요구 하는 방식

- 인터럽트 발생 시 문맥교환(Context Switching) 과정을 통해 인터럽트 서비스 프로그램 수행

- 주변 장치에 명령 송신 후 주변 장치로부터 결과를 피드백 받을 때 까지 CPU 는 다른 작업 수행 가능

- Programmed Driven I/O 의 문제점 개선

다. I/O 채널 프로세서

- DMA 개념을 확장하여 구현한 I/O 전용의 처리 장치를 이용 독자적인 프로세서를 가지는 형태

- CPU처럼 독자적으로 주 기억 장치에 저장된 명령어를 처리 가능

- CPU의 능동적인 개입 없이 입출력 처리 가능, 한 번에 하나의 I/O 장치를 제어 하는 선택 채널과 한번에 여러 I/O 장치를 제어 하는 다중화 채널의 형태가 존재

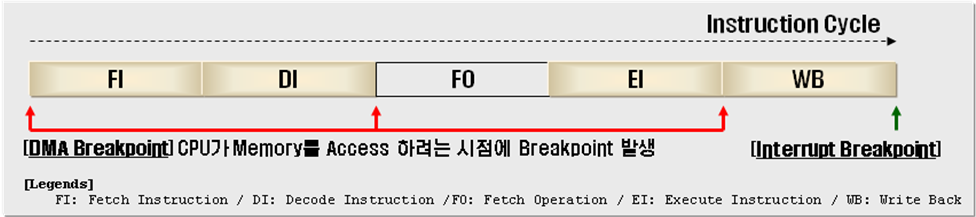

Ⅴ. DMA Breakpoint, DMA 데이터 전송유형 및 인터럽트와의 비교

가. DMA Breakpoint

나. DMA 데이터 전송유형

|

유형 |

Interrupt |

|

Burst Transfer |

DMA 제어기가 메모리 버스를 제어하는 동안 여러 개 메모리 WORD로 구성된 블록을 지속적으로 전송 |

|

Interleaved DMA |

CPU가 시스템 미사용시 DMA가 버스를 사용 |

|

Cycle Stealing |

DMA가 데이터 전송을 위해 프로세서의 한 메모리 Cycle을 중지 할 것을 요청 |

다. Cycle Stealing과 Interrupt의 비교

|

Cycle Stealing |

Interrupt |

|

한 Cycle 동안만 정지 프로그램의 상태를 보존할 필요가 없음 |

인터럽트가 해제될 때 까지 장기간 정지 중단된 프로그램의 상태보존이 필요하고, 인터럽트 처리 종료 후 프로그램을 원상태로 복원해야 함 |